# Ultralow Power, Rail-to-Rail Output Operational Amplifiers

# 0P281/0P481

### FEATURES

Low supply current: 4 µA/amplifier maximum Single-supply operation: 2.7 V to 12 V Wide input voltage range Rail-to-rail output swing Low offset voltage: 1.5 mV No phase reversal

#### **APPLICATIONS**

Comparator Battery-powered instrumentation Safety monitoring Remote sensors Low voltage strain gage amplifiers

### **GENERAL DESCRIPTION**

The OP281 and OP481 are dual and quad ultralow power single-supply amplifiers featuring rail-to-rail outputs. Each operates from supplies as low as 2.0 V and is specified at +3 V and +5 V single supplies as well as  $\pm 5$  V dual supplies.

Fabricated on Analog Devices' CBCMOS process, the OP281/OP481 feature a precision bipolar input and an output that swings to within millivolts of the supplies, continuing to sink or source current up to a voltage equal to the supply voltage.

Applications for these amplifiers include safety monitoring, portable equipment, battery and power supply control, and signal conditioning and interfacing for transducers in very low power systems.

The output's ability to swing rail-to-rail and not increase supply current when the output is driven to a supply voltage enables the OP281/OP481 to be used as comparators in very low power systems. This is enhanced by their fast saturation recovery time. Propagation delays are 250 µs.

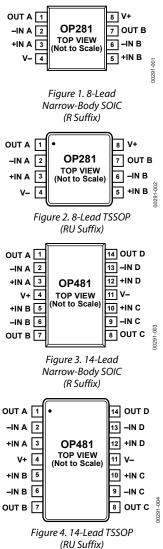

The OP281/OP481 are specified over the extended industrial temperature range (-40°C to +85°C). The OP281 dual amplifier is available in 8-lead SOIC surface-mount and TSSOP packages. The OP481 quad amplifier is available in narrow 14-lead SOIC and TSSOP packages.

### **PIN CONFIGURATIONS**

Rev. C Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©1996–2007 Analog Devices, Inc. All rights reserved.

## **TABLE OF CONTENTS**

| Features 1                          |

|-------------------------------------|

| Applications1                       |

| Pin Configurations                  |

| General Description                 |

| Revision History                    |

| Specifications                      |

| Electrical Specifications           |

| Absolute Maximum Ratings            |

| Thermal Resistance                  |

| ESD Caution                         |

| Typical Performance Characteristics |

| Applications                        |

### **REVISION HISTORY**

### 10/07—Rev. B to Rev. C

| Updated Format                            | Universal |

|-------------------------------------------|-----------|

| Changes to Offset Voltage Drift Condition |           |

| Changes to Slew Rate Symbol               | 5         |

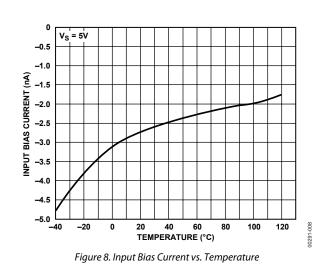

| Changes to Figure 8                       | 7         |

| Deleted SPICE Macro-Model Section         |           |

| Updated Outline Dimensions                | 17        |

| Changes to Ordering Guide                 |           |

| 3/03—Rev. A to Rev. B                     |           |

| Changes to Features                       | 1         |

| 2/03—Rev. 0 to Rev. A                     |           |

| Updated Format                            | Universal |

| Theory of Operation                            | 13 |

|------------------------------------------------|----|

| Input Overvoltage Protection                   | 13 |

| Input Offset Voltage                           |    |

| Input Common-Mode Voltage Range                | 13 |

| Capacitive Loading                             | 14 |

| Micropower Reference Voltage Generator         | 14 |

| Window Comparator                              | 14 |

| Low-Side Current Monitor                       | 15 |

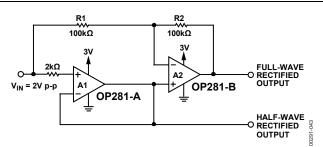

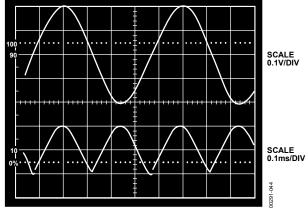

| Low Voltage Half-Wave and Full-Wave Rectifiers | 15 |

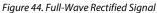

| Battery-Powered Telephone Headset Amplifier    | 15 |

| Outline Dimensions                             | 17 |

| Ordering Guide                                 | 18 |

| Deleted OP181                                       | .Universal  |

|-----------------------------------------------------|-------------|

| Updated Package Options                             | . Universal |

| Deleted OP181 Pin Configurations                    | 1           |

| Deleted Epoxy DIP Pin Configurations                | 1           |

| Changes to Absolute Maximum Ratings                 | 5           |

| Changes to Ordering Guide                           | 5           |

| Changes to Input Offset Voltage                     | 10          |

| Deleted Former Figure 33                            | 10          |

| Deleted Overdrive Recovery Time Section             | 11          |

| Deleted Former Figure 36                            | 11          |

| Deleted 8-Lead and 14-Lead Plastic DIP (N-8 and N-1 | 4)          |

| Outline Dimensions                                  | 14          |

| Updated Outline Dimensions                          | 14          |

### **SPECIFICATIONS**

### **ELECTRICAL SPECIFICATIONS**

$V_{\text{S}}$  = 3.0 V,  $V_{\text{CM}}$  = 1.5 V,  $T_{\text{A}}$  = 25°C, unless otherwise noted.

| Table 1.                     |                          |                                                                                                 |                                         |      |     |         |

|------------------------------|--------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------|------|-----|---------|

| Parameter                    | Symbol                   | Condition                                                                                       | Min                                     | Тур  | Max | Unit    |

| INPUT CHARACTERISTICS        |                          |                                                                                                 |                                         |      |     |         |

| Offset Voltage <sup>1</sup>  | Vos                      |                                                                                                 |                                         |      | 1.5 | mV      |

|                              |                          | $-40^\circ C \le T_A \le +85^\circ C$                                                           |                                         |      | 2.5 | mV      |

| Input Bias Current           | IB                       | $-40^{\circ}C \le T_{A} \le +85^{\circ}C$                                                       |                                         | 3    | 10  | nA      |

| Input Offset Current         | los                      | $-40^\circ C \le T_A \le +85^\circ C$                                                           |                                         | 0.1  | 7   | nA      |

| Input Voltage Range          |                          |                                                                                                 | 0                                       |      | 2   | V       |

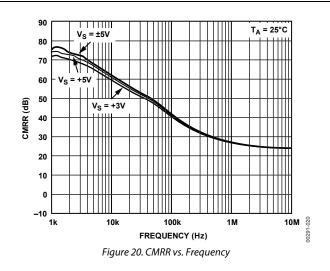

| Common-Mode Rejection Ratio  | CMRR                     | $V_{CM}$ = 0 V to 2.0 V, $-40^\circ C \leq T_A \leq +85^\circ C$                                | 65                                      | 95   |     | dB      |

| Large-Signal Voltage Gain    | Avo                      | $R_L$ = 1 MΩ, $V_O$ = 0.3 V to 2.7 V                                                            | 5                                       | 13   |     | V/mV    |

|                              |                          | $-40^{\circ}C \le T_{A} \le +85^{\circ}C$                                                       | 2                                       |      |     | V/mV    |

| Offset Voltage Drift         | $\Delta V_{OS}/\Delta T$ | -40°C to +85°C                                                                                  |                                         | 10   |     | μV/°C   |

| Bias Current Drift           | ΔΙ <sub>Β</sub> /ΔΤ      |                                                                                                 |                                         | 20   |     | pA/°C   |

| Offset Current Drift         | $\Delta I_{OS}/\Delta T$ |                                                                                                 |                                         | 2    |     | pA/°C   |

| OUTPUT CHARACTERISTICS       |                          |                                                                                                 |                                         |      |     |         |

| Output Voltage High          | V <sub>OH</sub>          | $R_L = 100 \text{ k}\Omega \text{ to GND}, -40^\circ\text{C} \le T_A \le +85^\circ\text{C}$     | 2.925                                   | 2.96 |     | V       |

| Output Voltage Low           | Vol                      | $R_L = 100 \text{ k}\Omega \text{ to V}+, -40^\circ\text{C} \le T_A \le +85^\circ\text{C}$      |                                         | 25   | 75  | mV      |

| Short-Circuit Limit          | lsc                      |                                                                                                 |                                         | ±1.1 |     | mA      |

| POWER SUPPLY                 |                          |                                                                                                 |                                         |      |     |         |

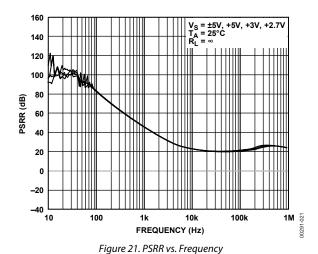

| Power Supply Rejection Ratio | PSRR                     | $V_{s} = 2.7 \text{ V to } 12 \text{ V}, -40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$ | 76                                      | 95   |     | dB      |

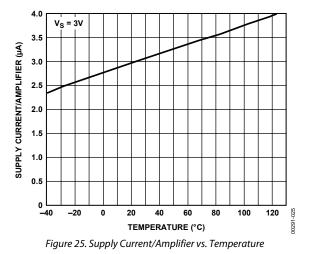

| Supply Current/Amplifier     | Isy                      | $V_0 = 0 V$                                                                                     |                                         | 3    | 4   | μA      |

|                              |                          | $-40^{\circ}C \le T_{A} \le +85^{\circ}C$                                                       |                                         |      | 5   | μA      |

| DYNAMIC PERFORMANCE          |                          |                                                                                                 |                                         |      |     |         |

| Slew Rate                    | SR                       | $R_{L} = 100 \text{ k}\Omega, C_{L} = 50 \text{ pF}$                                            |                                         | 25   |     | V/ms    |

| Turn-On Time                 |                          | $A_{V} = 1, V_{O} = 1 V$                                                                        |                                         | 40   |     | μs      |

|                              |                          | $A_V = 20, V_O = 1 V$                                                                           |                                         | 50   |     | μs      |

| Saturation Recovery Time     |                          |                                                                                                 |                                         | 65   |     | μs      |

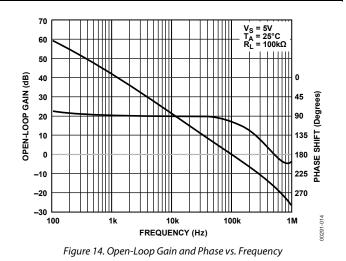

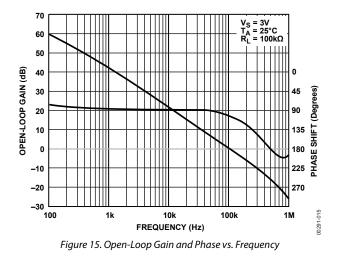

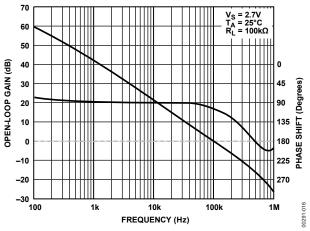

| Gain Bandwidth Product       | GBP                      |                                                                                                 |                                         | 95   |     | kHz     |

| Phase Margin                 | Фм                       |                                                                                                 |                                         | 70   |     | Degrees |

| NOISE PERFORMANCE            |                          |                                                                                                 | t i i i i i i i i i i i i i i i i i i i |      |     |         |

| Voltage Noise                | en p-p                   | 0.1 Hz to 10 Hz                                                                                 |                                         | 10   |     | μV p-p  |

| Voltage Noise Density        | en                       | f = 1 kHz                                                                                       |                                         | 75   |     | nV/√Hz  |

| Current Noise Density        | in                       |                                                                                                 |                                         | <1   |     | pA/√Hz  |

$^1\,\text{V}_{\text{OS}}$  is tested under a no load condition.

$V_{\text{S}}$  = 5.0 V,  $V_{\text{CM}}$  = 2.5 V,  $T_{\text{A}}$  = 25°C, unless otherwise noted.

### Table 2.

| Parameter                    | Symbol                   | Condition                                                                | Min   | Тур  | Max | Unit    |

|------------------------------|--------------------------|--------------------------------------------------------------------------|-------|------|-----|---------|

| INPUT CHARACTERISTICS        |                          |                                                                          |       |      |     |         |

| Offset Voltage <sup>1</sup>  | Vos                      |                                                                          |       | 0.1  | 1.5 | mV      |

|                              |                          | $-40^{\circ}C \le T_{A} \le +85^{\circ}C$                                |       |      | 2.5 | mV      |

| Input Bias Current           | IB                       | $-40^{\circ}C \le T_{A} \le +85^{\circ}C$                                |       | 3    | 10  | nA      |

| Input Offset Current         | los                      | $-40^{\circ}C \le T_{A} \le +85^{\circ}C$                                |       | 0.1  | 7   | nA      |

| Input Voltage Range          |                          |                                                                          | 0     |      | 4   | V       |

| Common-Mode Rejection Ratio  | CMRR                     | $V_{CM}$ = 0 V to 4.0 V, $-40^\circ C \leq T_A \leq +85^\circ C$         | 65    | 90   |     | dB      |

| Large-Signal Voltage Gain    | A <sub>vo</sub>          | $R_L$ = 1 MΩ, $V_O$ = 0.5 V to 4.5 V                                     | 5     | 15   |     | V/mV    |

|                              |                          | $-40^{\circ}C \le T_{A} \le +85^{\circ}C$                                | 2     |      |     | V/mV    |

| Offset Voltage Drift         | $\Delta V_{OS}/\Delta T$ | -40°C to +85°C                                                           |       | 10   |     | μV/°C   |

| Bias Current Drift           | $\Delta I_{B}/\Delta T$  |                                                                          |       | 20   |     | pA/°C   |

| Offset Current Drift         | $\Delta I_{OS}/\Delta T$ |                                                                          |       | 2    |     | pA/°C   |

| OUTPUT CHARACTERISTICS       |                          |                                                                          |       |      |     |         |

| Output Voltage High          | V <sub>OH</sub>          | $R_L = 100 \ k\Omega$ to GND, $-40^\circ C \le T_A \le +85^\circ C$      | 4.925 | 4.96 |     | V       |

| Output Voltage Low           | Vol                      | $R_L = 100 \ k\Omega$ to V+, $-40^\circ C \le T_A \le +85^\circ C$       |       | 25   | 75  | mV      |

| Short-Circuit Limit          | lsc                      |                                                                          |       | ±3.5 |     | mA      |

| POWER SUPPLY                 |                          |                                                                          |       |      |     |         |

| Power Supply Rejection Ratio | PSRR                     | $V_s = 2.7 V \text{ to } 12 V$ , $-40^{\circ}C \le T_A \le +85^{\circ}C$ | 76    | 95   |     | dB      |

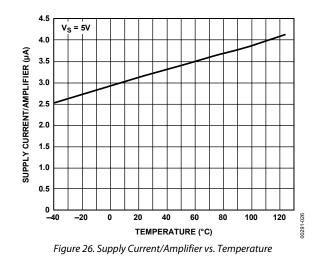

| Supply Current/Amplifier     | I <sub>SY</sub>          | $V_0 = 0 V$                                                              |       | 3.2  | 4   | μA      |

|                              |                          | $-40^{\circ}C \le T_{A} \le +85^{\circ}C$                                |       |      | 5   | μA      |

| DYNAMIC PERFORMANCE          |                          |                                                                          |       |      |     |         |

| Slew Rate                    | SR                       | $R_L = 100 \text{ k}\Omega, C_L = 50 \text{ pF}$                         |       | 27   |     | V/ms    |

| Saturation Recovery Time     |                          |                                                                          |       | 120  |     | μs      |

| Gain Bandwidth Product       | GBP                      |                                                                          |       | 100  |     | kHz     |

| Phase Margin                 | фм                       |                                                                          |       | 74   |     | Degrees |

| NOISE PERFORMANCE            |                          |                                                                          |       |      |     |         |

| Voltage Noise                | e <sub>n</sub> p-p       | 0.1 Hz to 10 Hz                                                          |       | 10   |     | μV p-p  |

| Voltage Noise Density        | en                       | f = 1 kHz                                                                |       | 75   |     | nV/√Hz  |

| Current Noise Density        | in                       |                                                                          |       | <1   |     | pA/√Hz  |

$^1\,\text{V}_{\text{OS}}$  is tested under a no load condition.

$V_{\text{S}}$  = ±5.0 V,  $T_{\text{A}}$  = +25°C, unless otherwise noted.

#### Table 3.

| Parameter                    | Symbol                   | Condition                                                                                               | Min    | Тур   | Max | Unit    |

|------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------|--------|-------|-----|---------|

| INPUT CHARACTERISTICS        |                          |                                                                                                         |        |       |     |         |

| Offset Voltage <sup>1</sup>  | Vos                      |                                                                                                         |        | 0.1   | 1.5 | mV      |

|                              |                          | $-40^{\circ}C \le T_{A} \le +85^{\circ}C$                                                               |        |       | 2.5 | mV      |

| Input Bias Current           | IB                       | $-40^\circ C \le T_A \le +85^\circ C$                                                                   |        | 3     | 10  | nA      |

| Input Offset Current         | los                      | $-40^\circ C \le T_A \le +85^\circ C$                                                                   |        | 0.1   | 7   | nA      |

| Input Voltage Range          |                          |                                                                                                         | -5     |       | +4  | V       |

| Common-Mode Rejection        | CMRR                     | $V_{CM} = -5.0 \text{ V to } +4.0 \text{ V}, -40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$     | 65     | 95    |     | dB      |

| Large-Signal Voltage Gain    | Avo                      | $R_L = 1 M\Omega, V_O = \pm 4.0 V,$                                                                     | 5      | 13    |     | V/mV    |

|                              |                          | $-40^\circ C \le T_A \le +85^\circ C$                                                                   | 2      |       |     | V/mV    |

| Offset Voltage Drift         | $\Delta V_{os}/\Delta T$ | -40°C to +85°C                                                                                          |        | 10    |     | μV/°C   |

| Bias Current Drift           | $\Delta I_{B}/\Delta T$  |                                                                                                         |        | 20    |     | pA/°C   |

| Offset Current Drift         | $\Delta I_{OS}/\Delta T$ |                                                                                                         |        | 2     |     | pA/°C   |

| OUTPUT CHARACTERISTICS       |                          |                                                                                                         |        |       |     |         |

| Output Voltage Swing         | Vo                       | $R_L = 100 \; k\Omega$ to GND, $-40^\circ C \leq T_A \leq +85^\circ C$                                  | ±4.925 | ±4.98 |     | V       |

| Short-Circuit Limit          | I <sub>sc</sub>          |                                                                                                         |        | 12    |     | mA      |

| POWER SUPPLY                 |                          |                                                                                                         |        |       |     |         |

| Power Supply Rejection Ratio | PSRR                     | $V_{S} = \pm 1.35 \text{ V to } \pm 6 \text{ V}, -40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$ | 76     | 95    |     | dB      |

| Supply Current/Amplifier     | lsy                      | $V_{O} = 0 V$                                                                                           |        | 3.3   | 5   | μA      |

|                              |                          | $-40^\circ C \le T_A \le +85^\circ C$                                                                   |        |       | 6   | μA      |

| DYNAMIC PERFORMANCE          |                          |                                                                                                         |        |       |     |         |

| Slew Rate                    | SR                       | $R_L = 100 \text{ k}\Omega, C_L = 50 \text{ pF}$                                                        |        | 28    |     | V/ms    |

| Gain Bandwidth Product       | GBP                      |                                                                                                         |        | 105   |     | kHz     |

| Phase Margin                 | фм                       |                                                                                                         |        | 75    |     | Degrees |

| NOISE PERFORMANCE            |                          |                                                                                                         |        |       |     |         |

| Voltage Noise                | en p-p                   | 0.1 Hz to 10 Hz                                                                                         |        | 10    |     | μV р-р  |

| Voltage Noise Density        | en                       | f = 1 kHz                                                                                               |        | 85    |     | nV/√Hz  |

|                              |                          | f = 10 kHz                                                                                              |        | 75    |     | nV/√Hz  |

| Current Noise Density        | İn                       |                                                                                                         |        | <1    |     | pA/√Hz  |

$^1\,V_{OS}$  is tested under a no load condition.

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 4.

| Parameter                                  | Rating           |

|--------------------------------------------|------------------|

| Supply Voltage                             | 16 V             |

| Input Voltage                              | GND to Vs + 10 V |

| Differential Input Voltage                 | ±3.5 V           |

| Output Short-Circuit Duration to GND       | Indefinite       |

| Storage Temperature Range                  | –65°C to +150°C  |

| Operating Temperature Range                | –40°C to +85°C   |

| Junction Temperature Range                 | –65°C to +150°C  |

| Lead Temperature Range (Soldering, 60 sec) | 300°C            |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### THERMAL RESISTANCE

#### Table 5. Thermal Resistance

| Package Type              | $\theta_{JA}^{1}$ | ον | Unit |

|---------------------------|-------------------|----|------|

| 8-Lead SOIC (R Suffix)    | 158               | 43 | °C/W |

| 8-Lead TSSOP (RU Suffix)  | 240               | 43 | °C/W |

| 14-Lead SOIC (R Suffix)   | 120               | 36 | °C/W |

| 14-Lead TSSOP (RU Suffix) | 240               | 43 | °C/W |

$^1$   $\theta_{JA}$  is specified for the worst-case conditions, that is,  $\theta_{JA}$  is specified for device soldered in circuit board for TSSOP and SOIC packages.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

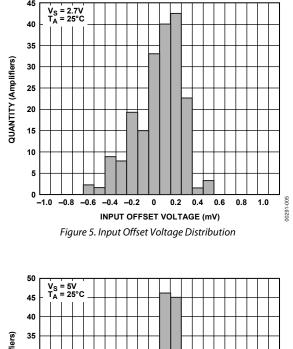

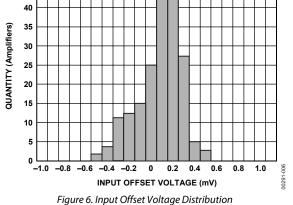

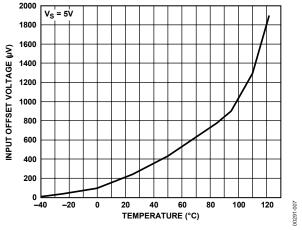

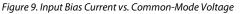

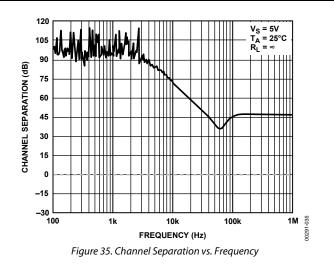

### **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 7. Input Offset Voltage vs. Temperature

1.0  $V_S = 5V$  $T_A = 25^{\circ}C$ 0.5 0 INPUT BIAS CURRENT (nA) -0.5 -1.0 -1.5 -2.0 -2.5 -3.0 -3.5 2.5 3.0 4.0 4.5 0 0.5 1.0 1.5 2.0 3.5 5.0 600-COMMON-MODE VOLTAGE (V) 00291-

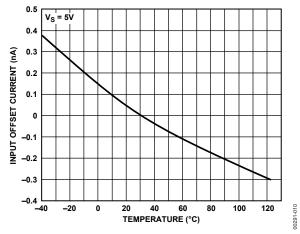

Figure 10. Input Offset Current vs. Temperature

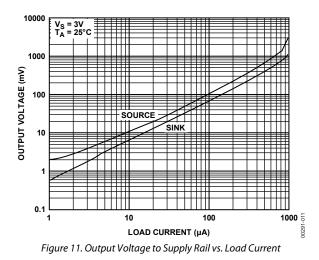

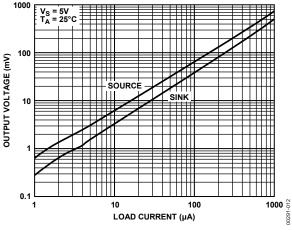

Figure 12. Output Voltage to Supply Rail vs. Load Current

Figure 13. Output Voltage to Supply Rail vs. Load Current

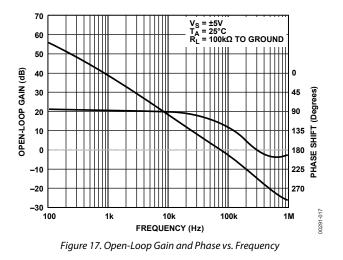

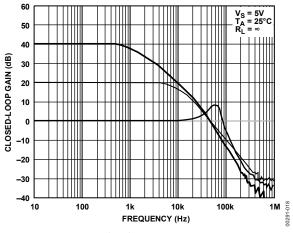

Figure 16. Open-Loop Gain and Phase vs. Frequency

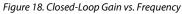

Figure 19. Voltage Noise Density vs. Frequency

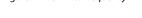

Figure 22. Small-Signal Overshoot vs. Load Capacitance

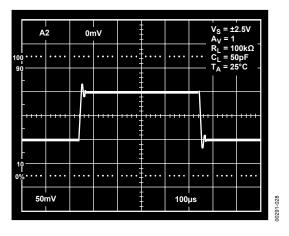

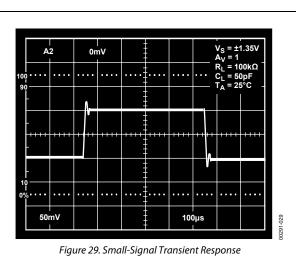

Figure 28. Small-Signal Transient Response

Figure 31. Large-Signal Transient Response

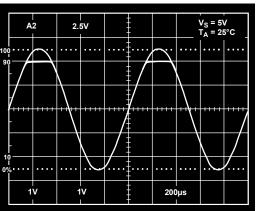

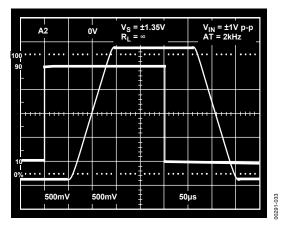

Figure 32. No Phase Reversal

00291-032

00291-031

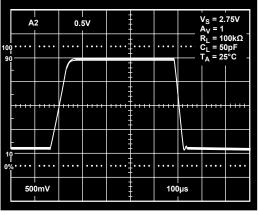

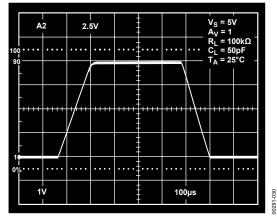

Figure 30. Large-Signal Transient Response

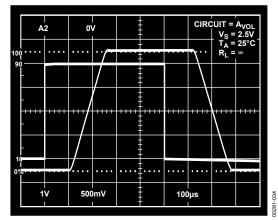

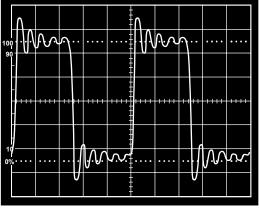

Figure 33. Saturation Recovery Time

Figure 34. Saturation Recovery Time

### APPLICATIONS THEORY OF OPERATION

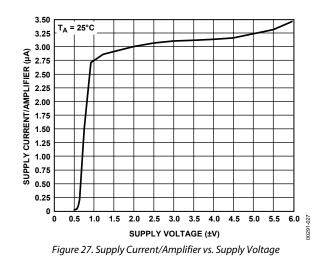

The OPx81 family of op amps is comprised of extremely low powered, rail-to-rail output amplifiers, requiring less than 4  $\mu$ A of quiescent current per amplifier. Many other competitors' devices may be advertised as low supply current amplifiers but draw significantly more current as the outputs of these devices are driven to a supply rail. The supply current of the OPx81 remains under 4  $\mu$ A even when the output is driven to either supply rail. Supply currents should meet the specification as long as the inputs and outputs remain within the range of the power supplies.

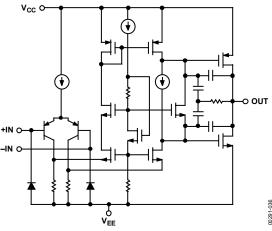

Figure 36 shows a simplified schematic of a single channel for the OPx81. A bipolar differential pair is used in the input stage. PNP transistors are used to allow the input stage to remain linear with the common-mode range extending to ground. This is an important consideration for single-supply applications. The bipolar front end also contributes less noise than a MOS front end with only nanoamps of bias currents. The output of the op amp consists of a pair of CMOS transistors in a common source configuration. This setup allows the output of the amplifier to swing to within millivolts of either supply rail. The headroom required by the output stage is limited by the amount of current being driven into the load. The lower the output current, the closer the output can go to either supply rail. Figure 11, Figure 12, and Figure 13 show the output voltage headroom vs. the load current. This behavior is typical of railto-rail output amplifiers.

Figure 36. Simplified Schematic of a Single OPx81 Channel

### INPUT OVERVOLTAGE PROTECTION

The input stage to the OPx81 family of op amps consists of a PNP differential pair. If the base voltage of either of these input transistors drops to more than 0.6 V below the negative supply, the input ESD protection diodes become forward-biased, and large currents begin to flow. In addition to possibly damaging the device, this creates a phase reversal effect at the output. To prevent this, the input current should be limited to less than 0.5 mA.

This can be done by simply placing a resistor in series with the input to the device. The size of the resistor should be proportional

to the lowest possible input signal excursion and can be found using the following formula:

$$R = \frac{V_{EE} - V_{IN,MIN}}{0.5 \times 10^{-3}}$$

where:

$V_{EE}$  is the negative power supply for the amplifier.  $V_{IN, MIN}$  is the lowest input voltage excursion expected.

For example, a single channel of the OPx81 should be used with a single-supply voltage of +5 V if the input signal may go as low as -1 V. Because the amplifier is powered from a single supply,  $V_{\text{EE}}$  is the ground; therefore, the necessary series resistance should be 2 k $\Omega$ .

### **INPUT OFFSET VOLTAGE**

The OPx81 family of op amps was designed for low offset voltages (less than 1 mV).

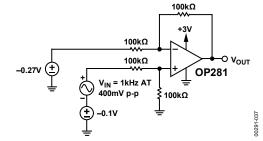

Figure 37. Single OPx81 Channel Configured as a Difference Amplifier Operating at  $V_{CM} < 0 V$

#### INPUT COMMON-MODE VOLTAGE RANGE

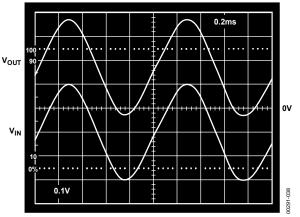

The OPx81 is rated with an input common-mode voltage range from  $V_{EE}$  to 1 V less than  $V_{CC}$ . However, the op amp can operate with a common-mode voltage that is slightly less than  $V_{EE}$ . Figure 37 shows a single OPx81 channel configured as a difference amplifier with a single-supply voltage of 3 V. Negative dc voltages are applied at both input terminals, creating a common-mode voltage that is less than ground. A 400 mV p-p input signal is then applied to the noninverting input. Figure 38 shows the resulting input and output waves. Notice how the output of the amplifier also drops slightly negative without distortion.

Figure 38. Input and Output Signals with  $V_{CM} < 0 V$

### **CAPACITIVE LOADING**

Most low supply current amplifiers have difficulty driving capacitive loads due to the higher currents required from the output stage for such loads. Higher capacitance at the output will increase the amount of overshoot and ringing in the amplifier's step response and may affect the stability of the device. However, through careful design of the output stage and its high phase margin, the OPx81 family can tolerate some degree of capacitive loading. Figure 39 shows the step response of a single channel with a 10 nF capacitor connected at the output. Notice that the overshoot of the output does not exceed more than 10% with such a load, even with a supply voltage of only 3 V.

Figure 39. Ringing and Overshoot of the Output of the Amplifier

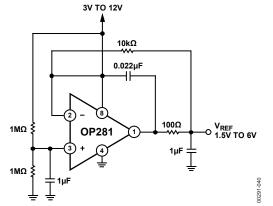

#### MICROPOWER REFERENCE VOLTAGE GENERATOR

Many single-supply circuits are configured with the circuit biased to half of the supply voltage. In these cases, a false ground reference can be created by using a voltage divider buffered by an amplifier. Figure 40 shows the schematic for such a circuit.

The two 1 M $\Omega$  resistors generate the reference voltage while drawing only 1.5  $\mu$ A of current from a 3 V supply. A capacitor connected from the inverting terminal to the output of the op amp provides compensation to allow a bypass capacitor to be connected at the reference output. This bypass capacitor helps to establish an ac ground for the reference output. The entire reference generator draws less than 5  $\mu$ A from a 3 V supply source.

Figure 40. Single Channel Configured as a Micropower Bias Voltage Generator

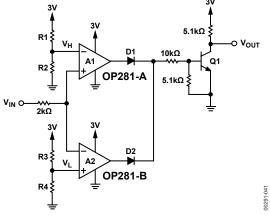

#### WINDOW COMPARATOR

The extremely low power supply current demands of the OPx81 family make it ideal for use in long-life battery-powered applications such as a monitoring system. Figure 41 shows a circuit that uses the OP281 as a window comparator.

Figure 41. Using the OP281 as a Window Comparator

The threshold limits for the window are set by  $V_{H}$  and  $V_{L}$ , provided that  $V_H > V_L$ . The output of the first OP281 (A1) will stay at the negative rail, in this case ground, as long as the input voltage is less than V<sub>H</sub>. Similarly, the output of the second OP281 (A2) will stay at ground as long the input voltage is higher than  $V_L$ . As long as  $V_{IN}$  remains between  $V_L$  and  $V_H$ , the outputs of both op amps will be 0 V. With no current flowing in either D1 or D2, the base of Q1 will stay at ground, putting the transistor in cutoff and forcing  $V_{\text{OUT}}$  to the positive supply rail. If the input voltage rises above V<sub>H</sub>, the output of A2 stays at ground, but the output of A1 goes to the positive rail and D1 conducts current. This creates a base voltage that turns on Q1 and drives  $V_{\text{OUT}}$  low. The same condition occurs if  $V_{\text{IN}}$  falls below V<sub>L</sub> with A2's output going high and D2 conducting current. Therefore, V<sub>OUT</sub> is high if the input voltage is between V<sub>L</sub> and V<sub>H</sub>, but low if the input voltage moves outside of that range.

The R1 and R2 voltage divider sets the upper window voltage, and the R3 and R4 voltage divider sets the lower voltage for the window. For the window comparator to function properly,  $V_H$  must be a greater voltage than  $V_L$ .

$$V_H = \frac{R2}{R1 + R2}$$

$$V_L = \frac{R4}{R3 + R4}$$

The 2 k $\Omega$  resistor connects the input voltage of the input terminals to the op amps. This protects the OP281 from possible excess current flowing into the input stages of the devices. D1 and D2 are small-signal switching diodes (1N4446 or equivalent), and Q1 is a 2N2222 or an equivalent NPN transistor.

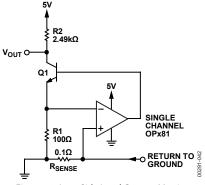

### LOW-SIDE CURRENT MONITOR

In the design of power-supply control circuits, a great deal of design effort is focused on ensuring the long-term reliability of a pass transistor over a wide range of load current conditions. As a result, monitoring and limiting device power dissipation is of primary importance in these designs. Figure 42 shows an example of a 5 V, single-supply current monitor that can be incorporated into the design of a voltage regulator with foldback current limiting or a high current power supply with crowbar protection. The design capitalizes on the OPx81's common-mode range extending to ground. Current is monitored in the power-supply return path, where a 0.1  $\Omega$ shunt resistor, R<sub>SENSE</sub>, creates a very small voltage drop. The voltage at the inverting terminal becomes equal to the voltage at the noninverting terminal through the feedback of Q1, which is a 2N2222 or an equivalent NPN transistor. This makes the voltage drop across R1 equal to the voltage drop across R<sub>SENSE</sub>. Therefore, the current through Q1 becomes directly proportional to the current through RSENSE, and the output voltage is given by the following equation:

$$V_{OUT} = V_{EE} - \left(\frac{R2}{R1} \times R_{SENSE} \times I_L\right)$$

The voltage drop across R2 increases as  $I_L$  increases; therefore,  $V_{\rm OUT}$  decreases if a higher supply current is sensed. For the element values shown, the  $V_{\rm OUT}$  transfer characteristic is -2.5 V/A, decreasing from  $V_{\rm EE}$ .

Figure 42. Low-Side Load Current Monitor

# LOW VOLTAGE HALF-WAVE AND FULL-WAVE RECTIFIERS

Because of its quick overdrive recovery time, an OP281 can be configured as a full-wave rectifier for low frequency (<500 Hz) applications. Figure 43 shows the schematic.

Figure 43. Single-Supply Full-Wave and Half-Wave Rectifiers Using an OP281

Amplifier A1 is used as a voltage follower that tracks the input voltage only when it is greater than 0 V. This provides a halfwave rectification of the input signal to the noninverting terminal of Amplifier A2. When A1's output is following the input, the inverting terminal of A2 also follows the input from the virtual ground between the inverting and noninverting terminals of A2. With no potential difference across R1, no current flows through either R1 or R2; therefore, the output of A2 also follows the input. When the input voltage goes below 0 V, the noninverting terminal of A2 becomes 0 V. This makes A2 work as an inverting amplifier with a gain of 1 and provides a full-wave rectified version of the input signal. A 2 k $\Omega$  resistor in series with A1's noninverting input protects the device when the input signal becomes less than ground.

# BATTERY-POWERED TELEPHONE HEADSET AMPLIFIER

Figure 45 shows how the OP281 can be used as a two-way amplifier in a telephone headset. One side of the OP281 can be used as an amplifier for the microphone, and the other side can be used to drive the speaker. A typical telephone headset uses a 600  $\Omega$  speaker and an electret microphone that requires a supply voltage and a biasing resistor.

Figure 45. Two-Way Amplifier in a Battery-Powered Telephone Headset

The OP281-A op amp provides about 29 dB of gain for audio signals coming from the microphone. The gain is set by the 300 k $\Omega$  and 11 k $\Omega$  resistors. The gain bandwidth product of the amplifier is 95 kHz, which yields a –3 dB rolloff at 3.4 kHz for the set gain of 28. This is acceptable because telephone audio is band limited for 300 kHz to 3 kHz signals. If higher gain is required for the microphone, an additional gain stage should be used, because adding more gain to the OP281 would limit the

audio bandwidth. A 2.2 k $\Omega$  resistor is used to bias the electret microphone. This resistor value may vary depending on the specifications of the microphone. The output of the microphone is ac-coupled to the noninverting terminal of the op amp. Two 1 M $\Omega$  resistors are used to provide the dc offset for single-supply use.

The OP281-B amplifier (see Figure 45) can provide up to 15 dB of gain for the headset speaker. Incoming audio signals are ac-coupled to a 10 k $\Omega$  potentiometer that is used to adjust the volume. Again, two 1 M $\Omega$  resistors provide the dc offset with a 1  $\mu$ F capacitor establishing an ac ground for the volume-control potentiometer. Because the OP281 is a rail-to-rail output amplifier, it would have difficulty driving a 600  $\Omega$  speaker directly. Here, a Class AB buffer is used to isolate the load from the amplifier and to provide the necessary current to drive the speaker. By placing the buffer in the feedback loop of the op amp, crossover distortion can be minimized. Q1 and Q2 should have minimum betas of 100. The 600  $\Omega$  speaker is ac-coupled to the emitters to prevent quiescent current from flowing into the speaker. The 1 µF coupling capacitor makes an equivalent high-pass filter cutoff at 265 Hz with a 600  $\Omega$ load attached. Again, this does not pose a problem because it is outside the frequency range for telephone audio signals.

The circuit in Figure 45 draws around 250  $\mu$ A of current. The Class AB buffer has a quiescent current of 140  $\mu$ A, and roughly 100  $\mu$ A is drawn by the microphone itself. A CR2032 3 V lithium battery has a life expectancy of 160 mA hours, which means this circuit can run continuously for 640 hours on a single battery.

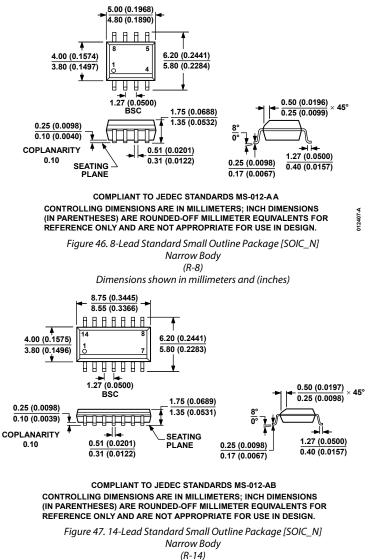

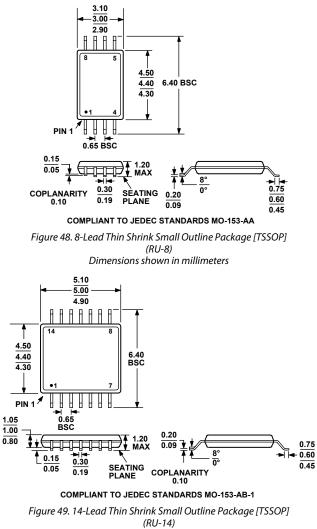

### **OUTLINE DIMENSIONS**

Dimensions shown in millimeters and (inches)

0 60 606-A

Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model                       | Temperature Range | Package Description | Package Option |

|-----------------------------|-------------------|---------------------|----------------|

| OP281GRU-REEL               | -40°C to +85°C    | 8-Lead TSSOP        | RU-8           |

| OP281GRUZ-REEL <sup>1</sup> | –40°C to +85°C    | 8-Lead TSSOP        | RU-8           |

| OP281GS                     | –40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| OP281GS-REEL                | –40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| OP281GS-REEL7               | –40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| OP281GSZ <sup>1</sup>       | –40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| OP281GSZ-REEL <sup>1</sup>  | –40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| OP281GSZ-REEL71             | –40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| OP481GRU-REEL               | –40°C to +85°C    | 14-Lead TSSOP       | RU-14          |

| OP481GRUZ-REEL <sup>1</sup> | –40°C to +85°C    | 14-Lead TSSOP       | RU-14          |

| OP481GS                     | –40°C to +85°C    | 14-Lead SOIC_N      | R-14           |

| OP481GS-REEL                | –40°C to +85°C    | 14-Lead SOIC_N      | R-14           |

| OP481GS-REEL7               | –40°C to +85°C    | 14-Lead SOIC_N      | R-14           |

| OP481GSZ <sup>1</sup>       | –40°C to +85°C    | 14-Lead SOIC_N      | R-14           |

| OP481GSZ-REEL <sup>1</sup>  | –40°C to +85°C    | 14-Lead SOIC_N      | R-14           |

| OP481GSZ-REEL71             | –40°C to +85°C    | 14-Lead SOIC_N      | R-14           |

$^{1}$  Z = RoHS Compliant Part.

### NOTES

### NOTES

www.analog.com

©1996–2007 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D00291-0-10/07(C)

Rev. C | Page 20 of 20